# TMS7000 Family Data Manual

8-bit Microcomputer Family

#### IMPORTANT NOTICE

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

Texas Instruments assumes no responsibility for infringement of patents or rights of others based on Texas Instruments applications assistance or product specifications, since TI does not possess full access to data concerning the use or applications of customer's products. TI also assumes no responsibility for customer product designs.

Copyright © 1983 by Texas Instruments Incorporated

# **TABLE OF CONTENTS**

| SECTIO | N      |           |              |                                  |                                         |         |      | PAGE |

|--------|--------|-----------|--------------|----------------------------------|-----------------------------------------|---------|------|------|

| 1.     | INTROI | DUCTION   |              |                                  |                                         |         |      |      |

|        | 1.1    |           |              |                                  |                                         |         | <br> | 1-1  |

|        | 1.2    |           |              | sign Philosophy                  |                                         |         |      | 1-1  |

|        |        | 1.2.1     |              | Architecture To                  |                                         |         |      |      |

|        |        | 1.2.2     | Microprog    | ramming                          |                                         |         | <br> | 1-3  |

|        | 1.3    |           | ires Of The  | TMS7000 Fam                      | ilv                                     |         | <br> | 1-4  |

|        | 1.4    | Support   | 3100 01 1110 |                                  |                                         |         | <br> | 1-6  |

|        | 1.4    | 1.4.1     |              | ent Tools                        |                                         |         |      |      |

|        |        | 1.4.2     | Hotline As   | sistance                         |                                         |         |      | 1-7  |

|        |        | 1.4.3     |              | apport                           |                                         |         |      |      |

|        |        | 1.4.0     |              | TDC-700-TMS7                     |                                         |         |      |      |

|        |        |           |              | ATS-710-TMS7                     |                                         |         |      |      |

|        |        | 1.4.4     |              | pertise                          |                                         |         |      |      |

|        |        | 1.7.7     | Design LA    | Jeruse                           |                                         |         | <br> |      |

| 2.     |        |           | Y ARCHITI    |                                  |                                         |         |      | 0.0  |

|        | 2.1    |           |              | egisters                         |                                         |         |      |      |

|        |        | 2.1.1     |              | le (RF)                          |                                         |         |      |      |

|        |        | 2.1.2     |              | File (PF)                        |                                         |         |      |      |

|        |        | 2.1.3     |              | ter (SP)                         |                                         |         |      |      |

|        |        | 2.1.4     |              | gister (ST)                      |                                         |         |      |      |

|        |        | 2.1.5     |              | Counter (PC)                     |                                         |         |      |      |

|        | 2.2    | On-Chip ( | General Pur  | pose I/O Ports                   |                                         |         | <br> | 2-4  |

|        | 2.3    | •         |              |                                  |                                         |         |      |      |

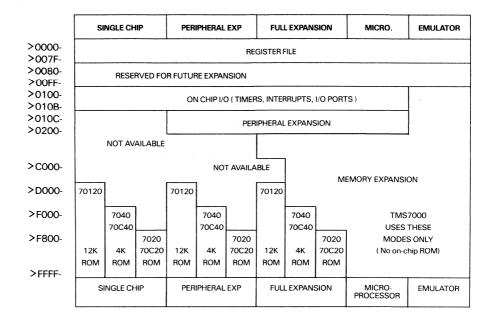

|        |        | 2.3.1     |              | p Mode                           |                                         |         |      |      |

|        |        | 2.3.2     |              | Expansion Mod                    |                                         |         |      |      |

|        |        | 2.3.3     | Full Expan   | sion Mode                        |                                         |         | <br> | 2-14 |

|        |        | 2.3.4     | Microproc    | essor Mode                       | • • • • • • • • • • •                   |         | <br> | 2-14 |

|        |        | 2.3.5     |              | mulator Mode .                   |                                         |         |      |      |

|        | 2.4    |           |              | 3                                |                                         |         |      |      |

|        | 2.5    |           |              | Clock Options .                  |                                         |         |      |      |

|        |        | 2.5.1     |              | Priority                         |                                         |         |      |      |

|        |        | 2.5.2     |              | tialization<br>face To Interrupt |                                         |         |      |      |

|        |        | 2.5.3     |              | .ogic                            |                                         |         |      |      |

|        | 2.6    | 2.5.4     | interrupt i  | r/Event Counter                  | · · · · · · · · · · · · · · · · · · ·   |         | <br> | 2-24 |

|        | 2.6    | 2.6.1     |              | Clock (RTC)                      |                                         |         |      |      |

|        |        | 2.6.2     |              | inter (EC)                       |                                         |         |      |      |

|        |        | 2.6.3     |              | Prescaled Cloc                   |                                         |         |      |      |

|        |        | 2.6.4     |              | rrupt Pulse                      |                                         |         |      |      |

|        |        | 2.6.5     |              |                                  |                                         |         |      |      |

|        |        | 2.6.6     |              | th Measuremen                    |                                         |         |      |      |

|        |        | 2.6.7     |              | th Modulation (                  |                                         |         |      |      |

|        |        | 2.6.8     | Multi-Inte   | rrupt Pulse Widt                 | h Modulation (F                         | PWM)    | <br> | 2-31 |

|        | 2.7    |           | rt (TMS70)   | K1 Versions Onl                  | (1) (1) (1) (1) (1) (1) (1) (1) (1) (1) | •••••   | <br> | 2-33 |

|        | 2.7    | 2.7.1     |              | on                               |                                         |         |      |      |

|        |        | 2.7.2     |              | rces And Serial                  |                                         |         |      |      |

|        |        |           | 2.7.2.1      | Asynchronous                     | Communication                           | n Mode  | <br> | 2-35 |

|        |        |           | 2.7.2.2      | Isosynchronous                   | S Communication                         | on Mode | <br> | 2-36 |

|        |        |           |              | Serial I/O Comp                  |                                         |         |      |      |

|    |     | 2.7.3      | Multiprocessor Communication 2-3                 |

|----|-----|------------|--------------------------------------------------|

|    |     |            | 2.7.3.1 Motorola (MC6801) Protocol 2-3           |

|    |     |            | 2.7.3.2 Intel (I8051) Protocol                   |

|    |     | 2.7.4      | Timer 3                                          |

|    |     | 2.7.5      | Serial Port Registers                            |

|    |     |            | 2.7.5.1 Mode Register (SMODE)                    |

|    |     |            | 2.7.5.2 Serial Control O Register (SCTLO)        |

|    |     |            | 2.7.5.3 Serial Port Status Register (SSTAT)      |

|    |     |            | 2.7.5.4 Serial Control 1 Register (SCTL1)        |

|    |     |            | 2.7.5.5 Timer 3 Data Register                    |

|    |     |            | 2.7.5.6 Receiver Buffer                          |

|    |     |            |                                                  |

|    |     | 2.7.6      | 2.7.5.7       Transmitter Buffer                 |

|    |     | 2.7.7      | Carial Part Interrupt                            |

|    | 2.8 |            | Serial Port Interrupt                            |

|    | 2.0 | Pin Desi   | cription                                         |

| 3. |     |            | STRUCTION SET                                    |

|    | 3.1 | Definition | ons                                              |

|    | 3.2 | Address    | sing Modes                                       |

|    |     | 3.2.1      | Direct Addressing Modes                          |

|    |     |            | 3.2.1.1 Single Register Addressing Mode          |

|    |     |            | 3.2.1.2 Register File Addressing Mode            |

|    |     |            | 3.2.1.3 Peripheral File Addressing Mode          |

|    |     |            | 3.2.1.4 Immediate Addressing Mode                |

|    |     |            | 3.2.1.5 Program Counter Relative Addressing Mode |

|    |     | 3.2.2      | Extended Addressing Modes                        |

|    |     |            | 3.2.2.1 Direct Memory Addressing                 |

|    |     |            | 3.2.2.2 Register File Indirect Addressing Mode   |

|    |     |            | 3.2.2.3 Indexed Addressing Mode                  |

|    | 3.3 | Instructi  | ions                                             |

|    | 0.0 | 3.3.1      | Implied Operand Instructions 3-8                 |

|    |     | 3.3.2      | Single Operand Instructions                      |

|    |     | 3.3.3      | Dual Operand Instructions                        |

|    |     | 3.3.3      | Dual Operand Instructions                        |

|    |     |            | , pos 1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,     |

|    |     | 3.3.4      |                                                  |

|    |     | 3.3.4      | Jump Instructions                                |

|    |     |            | 3.3.4.1 Simple Relative Instruction Type         |

|    |     |            | 3.3.4.2 Single Relative Instruction Type         |

|    |     |            | 3.3.4.3 Dual Relative Instruction Type           |

|    |     |            | 3.3.4.4 Peripheral Relative Instruction Type     |

|    |     | 3.3.5      | Extended Address Instructions                    |

|    |     | 3.3.6      | Miscellaneous Instructions                       |

|    |     |            | 3.3.6.1 MOVD Instruction                         |

|    |     |            | 3.3.6.2 TRAP Instructions                        |

|    | 3.4 | Custom     | Microcoding                                      |

|    | 3.5 |            | ion Descriptions                                 |

|    |     | 3.5.1      | ADC - Add With Carry                             |

|    |     | 3.5.2      | ADD - Add                                        |

|    |     | 3.5.3      | AND - And                                        |

|    |     | 3.5.4      | ANDP - And Peripheral Register                   |

|    |     | 3.5.5      | BTJO - Bit Test And Jump If One                  |

|    |     | 3.5.6      | BTJOP - Bit Test And Jump If One Peripheral      |

|    |     | 3.5.7      | BTJZ - Bit Test And Jump If Zero                 |

|    | 3.5.8        | BTJZP - Bit Test And Jump If One Peripheral         | 3-25   |

|----|--------------|-----------------------------------------------------|--------|

|    | 3.5.9        | BR - Branch                                         | 3-25   |

|    | 3.5.10       | CALL - Call                                         | 3-26   |

|    | 3.5.11       | CLR - Clear                                         | 3-26   |

|    | 3.5.12       | CLRC - Clear The Carry Bit                          | 3-27   |

|    | 3.5.13       | CMP - Compare                                       | 3-27   |

|    | 3.5.14       | CMPA - Compare Accumulator Extended                 | 3-27   |

|    | 3.5.15       | DAC - Decimal Add With Carry                        | 3-28   |

|    | 3.5.16       | DEC - Decrement                                     | 3-28   |

|    | 3.5.17       | DECD - Decrement Double                             | 3-29   |

|    | 3.5.18       | DINT - Disable Interrupts                           | 3-29   |

|    | 3.5.19       | DJNZ - Decrement Register And Jump If Not Zero      | 3-30   |

|    | 3.5.20       | DSB - Decimal Subtract With Borrow                  | 3-30   |

|    | 3.5.21       | EINT - Enable Interrupts                            | 3-31   |

|    | 3.5.22       | IDLE - Idle Until Interrupt                         | 3-31   |

|    | 3.5.23       | INC - Increment                                     | 3-32   |

|    | 3.5.24       | INV - Invert                                        | 3-32   |

|    | 3.5.25       | JMP - Jump Unconditional                            | 3-33   |

|    | 3.5.26       | J < cnd > - Jump On Condition                       | 3-33   |

|    | 3.5.27       | LDA - Load A Register                               | 3-34   |

|    | 3.5.28       | LDSP - Load Stack Pointer                           | 3-35   |

|    | 3.5.29       | MOV - Move                                          | 3-35   |

|    | 3.5.30       | MOVD - Move Double                                  | 3-30   |

|    | 3.5.31       | MOVP - Move To/From Peripheral File                 | 3-30   |

|    | 3.5.32       | MPY - Multiply                                      | 3-3/   |

|    | 3.5.33       | NOP - No Operation                                  | 3-3/   |

|    | 3.5.34       | OR - Or                                             | 3-38   |

|    | 3.5.35       | OPR - Or Peripheral File Register                   | 3-38   |

|    | 3.5.36       | POP - Pop From Stack                                | . 3-39 |

|    | 3.5.37       | PUSH - Push On Stack                                | . 3-39 |

|    | 3.5.38       | RETI - Return From Interrupt                        | . 3-40 |

|    | 3.5.39       | RETS - Return From Subroutine                       | . 3-40 |

|    | 3.5.40       | RL - Rotate Left                                    | . 3-41 |

|    | 3.5.41       | RLC - Rotate Left Through Carry                     | . 3-41 |

|    | 3.5.42       | RR - Rotate Right                                   | . 3-42 |

|    | 3.5.43       | RRC - Rotate Right Through Carry                    | . 3-42 |

|    | 3.5.44       | SBB - Subtract With Borrow                          | . 3-43 |

|    | 3.5.45       | SETC - Set Carry                                    | . 3-43 |

|    | 3.5.46       | STA - Store A Register                              | . 3-44 |

|    | 3.5.47       | STSP - Store Stack Pointer                          | . 3-44 |

|    | 3.5.48       | SUB - Subtract                                      | . 3-45 |

|    | 3.5.49       | SWAP - Swap Nibbles                                 | . 3-45 |

|    | 3.5.50       | TRAP - Trap To Subroutine                           | . 3-46 |

|    | 3.5.51       | TSTA - Test A Register                              | . 3-47 |

|    | 3.5.52       | TSTB - Test B Register                              | . 3-4  |

|    | 3.5.53       | XCHB - Exchange with B Register                     | . 3-4  |

|    | 3.5.54       | XOR - Exclusive Or                                  | . 3-48 |

|    | 3.5.55       | XORP - Exclusive Or Peripheral File                 | . 3-48 |

| 4. | ELECTRICAL S | PECIFICATIONS                                       |        |

|    |              | 00/TMS7020/TMS7040/TMS70120/TMS7001/TMS7041         | . 4-1  |

|    | 4.1.1        | Description Of The TMS7000/TMS7020/TMS7040/TMS70120 | 4.4    |

|    |              | TMS7001/TMS7041 Devices                             | . 4-1  |

|    |              |                                                     |        |

|    |      | 4.1.2        | Rey reatures                                                        | 4-2          |

|----|------|--------------|---------------------------------------------------------------------|--------------|

|    |      | 4.1.3        | Absolute Maximum Ratings Over Operating Free-Air Temperature        | –            |

|    |      |              | Range                                                               | 4-3          |

|    |      | 4.1.4        | Recommended Operating Conditions                                    | 4-3          |

|    |      | 4.1.5        | Electrical Characteristics Over Full Range Of Operating Conditions  | <b>1</b> -3  |

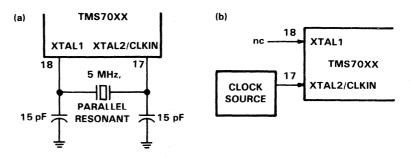

|    |      | 4.1.6        | Recommended Crystal/Clockin Operating Conditions Over Full          | 4-3          |

|    |      |              | Operating Range                                                     | 4.4          |

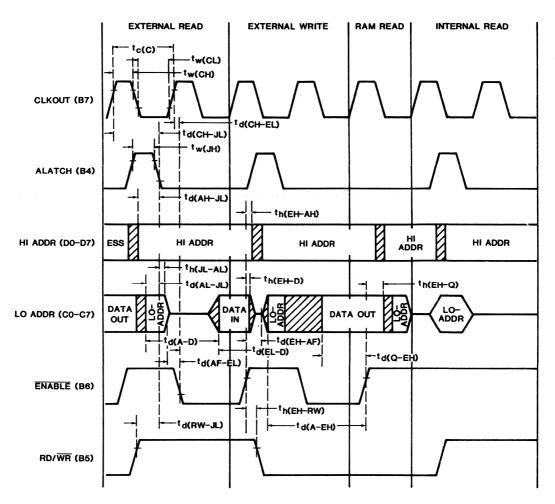

|    |      | 4.1.7        | Memory Interface Timing At 10MHz Over Full Operating Free Air       | 4-4          |

|    |      |              | Temporature Range                                                   |              |

|    |      | 4.1.8        | Temperature Range                                                   | 4-5          |

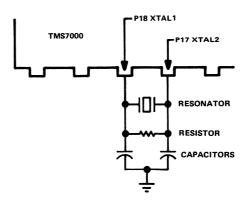

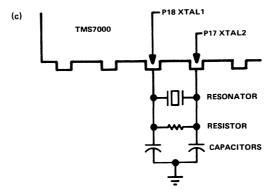

|    |      | 4.1.9        | Application Of Ceramic Resonator                                    | 4-7          |

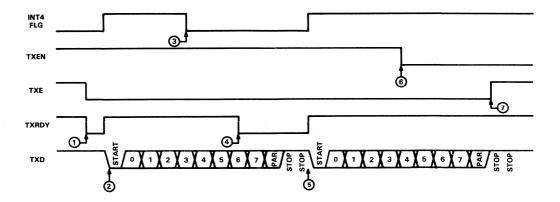

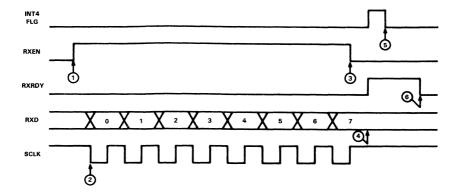

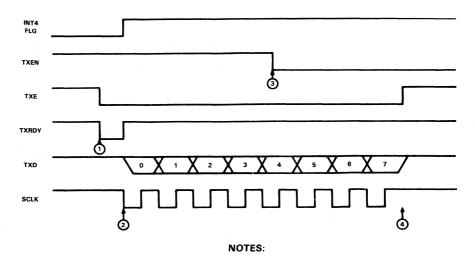

|    |      | 4.1.9        | Serial Port Timing                                                  | 4-8          |

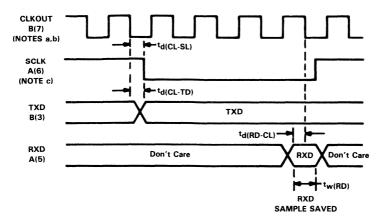

|    |      |              | 4.1.9.1 Internal Serial Clock                                       | 4-8          |

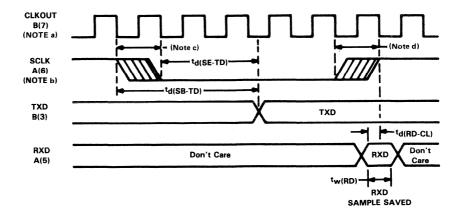

|    |      |              | 4.1.9.2 External Serial Clock                                       | 4-9          |

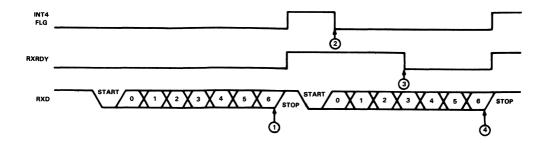

|    |      |              | 4.1.9.3 RX Signals In Communication Modes                           | 4-10         |

|    |      |              | 4.1.9.4 TX Signals In Communication Modes                           | 4-11         |

|    |      |              | 4.1.9.5 RX Signals In Serial I/O Mode                               | 4-12         |

|    |      |              | 4.1.9.6 TX Signals In Serial I/O Mode                               | 4-13         |

|    |      | 4.1.10       | Pin Descriptions                                                    | 4-14         |

|    |      |              | 4.1.10.1 Pin Descriptions Of The TMS7000/TMS7020/TMS7040            |              |

|    |      |              | TMS70120                                                            | 4-14         |

|    |      |              | 4.1.10.2 Pin Descriptions Of The TMS7001/TMS7041                    | 4-15         |

|    | 4.2  | TMS700       | C00/TMS70C20/TMS70C40                                               | 4-16         |

|    |      | 4.2.1        | Description Of The TMS70C00/TMS70C20/TMS70C40                       | <i>1</i> -16 |

|    |      | 4.2.2        | Key Features                                                        | 4 17         |

|    |      | 4.2.3        | Absolute Maximum Rating Over Operating Free-Air Temperature         | 4-,17        |

|    |      |              | Range                                                               | 1 10         |

|    |      | 4.2.4        | Recommended Operating Conditions                                    | 4-10         |

|    |      | 4.2.5        | Electrical Characteristics Over Full Range of Operating Conditions  | 4-18         |

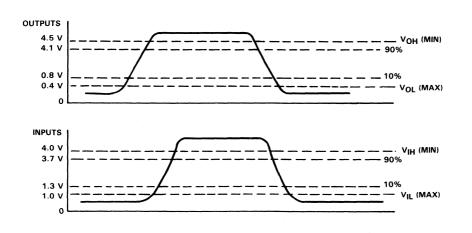

|    |      | 4.2.6        | AC Characteristics For Input/Output Bases                           | 4-18         |

|    |      | 4.2.7        | AC Characteristics For Input/Output Ports                           | 4-19         |

|    |      | 4.2.7        | Recommended Crystal/Clockin Operating Conditions Over Full          |              |

|    |      | 400          | Operating Range                                                     | 4-19         |

|    |      | 4.2.8        | Memory Interface Timing At VDD = 5V, FOSC = 3MHz Over               |              |

|    |      | 4.0.0        | The Full Operating Free-Air Temperature Range                       | 4-21         |

|    |      | 4.2.9        | Pin Descriptions Of The TMS70C00/TMS70C20/TMS70C40                  | 4-24         |

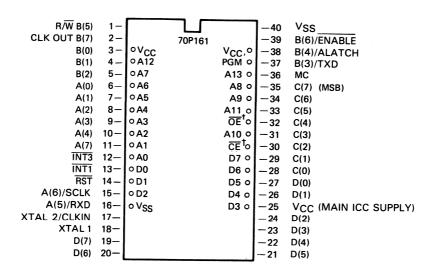

|    | 4.3  | SE70P10      | 61                                                                  | 4-25         |

|    |      | 4.3.1        | Description Of The SE70P161 Prototyping Component                   | 4-25         |

|    |      | 4.3.2        | Prototyping                                                         | 4-25         |

|    |      |              | 4.3.2.1 TMS7041 Prototyping                                         | 4-25         |

|    |      |              | 4.3.2.2 TMS7020/TMS7040/TMS70120 Prototyping                        | 4-25         |

|    |      | 4.3.3        | Programming And Installing Eproms                                   | 4-26         |

|    |      | 4.3.4        | Absolute Maximum Ratings Over Operating Free-Air Temperature        | 0            |

|    |      |              | Range                                                               | 1-26         |

|    |      | 4.3.5        | Recommended Operating Conditions                                    | 1 27         |

|    |      | 4.3.6        | Electrical Characteristics Over Full Range Of Operating Conditions. | 4 27         |

|    |      | 4.3.7        | Recommended Crystal/Clockin Operating Conditions Over Full          | 4-27         |

|    |      |              | Operating Range                                                     | 4.07         |

|    |      | 4.3.8        | Memory Interface Timing At 10MHz Over Full Operating Free-Air       | 4-27         |

|    |      | 1.0.0        | Temperature Page                                                    |              |

|    |      | 4.3.9        | Temperature Range                                                   | 4-28         |

|    |      | T.U.U        | Pin Description Of The SE70P161                                     | 4-30         |

| 5. | MICE |              | MMINIC                                                              |              |

| J. | 5.1  | OPROGRA      |                                                                     |              |

|    | ວ. ເ | 1 IVI 5 / UU | 00 Custom Microcoding Description                                   | 5-1          |

|    |      | 5.1.1        | Typical Applications                                                | 5-1          |

|    |      |              |                                                                     |              |

|     | 5.1.2   | Key Features                                           |           |

|-----|---------|--------------------------------------------------------|-----------|

|     | 5.1.3   | Microcoding Example 5-5                                |           |

|     | 5.1.4   | Tradeoffs Of Microcoding                               |           |

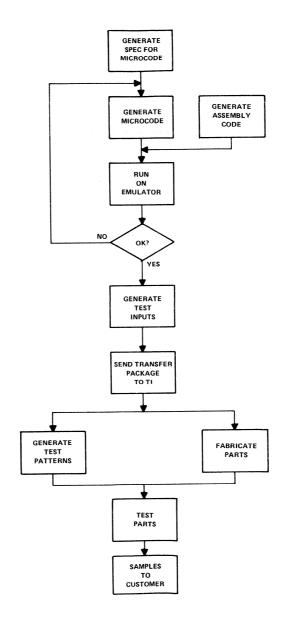

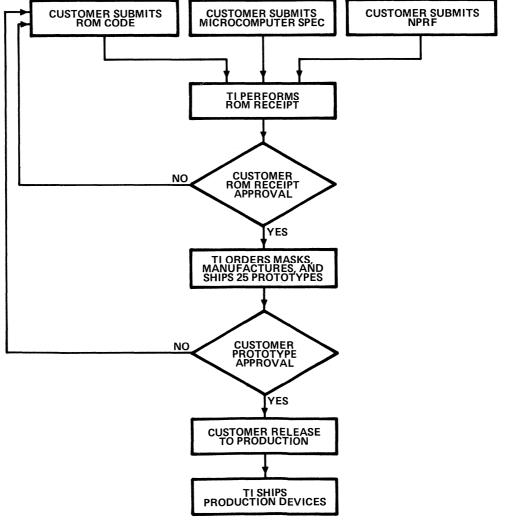

|     | 5.1.5   | Microcode Development Cycle                            |           |

|     | 5.1.6   | Available Support                                      |           |

|     |         | 5.1.6.1 TMS7000 Microassembler Software Package 5-8    |           |

|     |         | 5.1.6.2 TMS7000 AMPL Emulator System 5-8               |           |

|     |         | 5.1.6.3 TMS7000 Microcode Documentation Package 5-8    |           |

| 5.2 | Microco | ded Benchmarks                                         |           |

| 0   | 5.2.1   | Benchmark Rules                                        |           |

|     | 5.2.2   | Benchmark 1: 16 Bit Binary Addition                    | )         |

|     | 5.2.3   | Benchmark 2: 16 Bit Binary Coded Decimal Addition 5-10 | 2         |

|     | 5.2.4   | Benchmark 3: Block Move                                | 1         |

|     | 5.2.5   | Benchmark 4: Table Search                              | 2         |

|     | 5.2.6   | Benchmark 5: Binary To BCD Conversion                  | 3         |

|     | 5.2.7   | Benchmark 6: Bit I/O                                   | 4         |

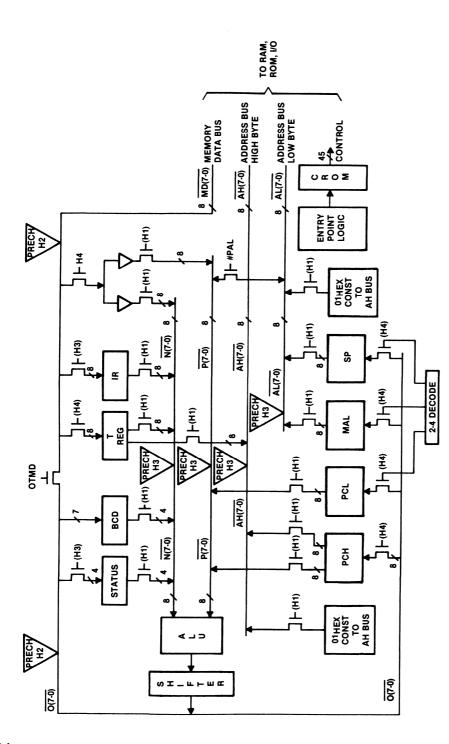

| 5.3 | Microse | chitecture Description                                 | 5         |

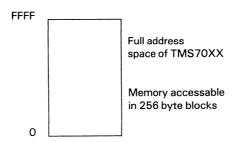

| 5.3 | 5.3.1   | TMS7000 Family Address Space                           | 5         |

|     | 5.3.1   | Basic TMS7000 Architecture                             | 6         |

|     |         | Microinstruction Format                                | 8         |

|     | 5.3.3   | 5.3.3.1 Microinstruction Cycle Timing                  | ō         |

|     |         | 5.3.3.2 Memory Cycle Timing                            | 1         |

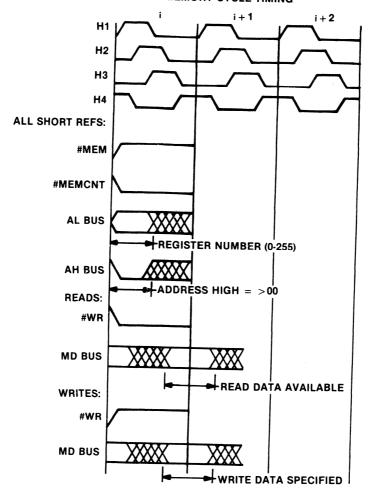

|     |         | 5.3.3.3 Short Memory References                        | 1         |

|     |         | r o                                                    | •         |

|     |         |                                                        | 4         |

|     |         |                                                        | 5         |

|     | - 0 4   | 5.3.3.6 Memory Control Signals                         |           |

|     | 5.3.4   |                                                        | -         |

|     |         | F 0                                                    |           |

|     |         | F 0                                                    | -         |

|     |         | F 0                                                    | _         |

|     |         | 3.3.4.4 All Dus                                        |           |

|     |         | 5.5.4.5 O bus                                          |           |

|     |         | 5.3.4.6 MD Bus                                         |           |

|     |         | 5,5,4,7 ALO Operation                                  | _         |

|     |         |                                                        | -         |

|     |         | J.J.7.J 11110gistoi                                    |           |

|     |         |                                                        |           |

|     |         | 5.3.4.10.1 (STC) Status Carry Bit 5-3                  |           |

|     |         | 5.3.3.10.2 STSB - Status Sign Bit                      |           |

|     |         | 5.3.3.10.3 STEZ - Status Equal To Zero Bit 5-3         |           |

|     |         | 5.3.3.10.4 STINT - Status Interrupt Enable Bit 5-4     |           |

|     |         | 5.3.4.11 BCD Constant Register                         |           |

|     |         | 5.3.4.12 Other Registers                               | ۱3<br>• • |

|     | 5.3.5   | Microinstruction Sequence Control Overview             |           |

|     |         | 5.3.5.1 Dispatch Conditions                            | ₽5        |

|     |         | 5.3.5.1.1 Unconditional Branching - JUNC 5-4           | ₽5        |

|     |         | 5.3.5.1.2 Function Dispatch - IRL                      |           |

|     |         | 5.3.5.1.3 Test Sign Bit - JT7                          |           |

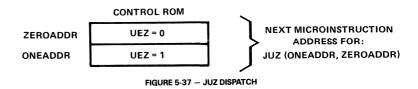

|     |         | 5.3.5.1.4 Test If Zero - JUZ                           |           |

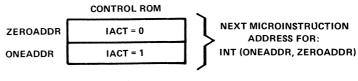

|     |         | 5.3.5.1.5 Test If Interrupt - INT                      |           |

|     |         | 5.3.5.1.6 Group Dispatch - IRH 5-4                     |           |

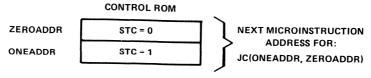

|     |         | 5.3.5.1.7 Test If Carry - JC                           |           |

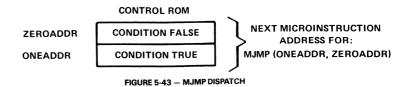

|     |         | 5.3.5.1.8 Test Status Register - MJMP 5-8              |           |

|     | 5.3.6   | Reset Operation                                        | 51        |

| Ο. | DESI | GUIA NIDS |                                                                 |     |

|----|------|-----------|-----------------------------------------------------------------|-----|

|    | 6.1  | Interfa   | cing The TMS7000 To Peripheral And Memory Devices 6             | - 1 |

|    |      | 6.1.1     | Introduction                                                    | -1  |

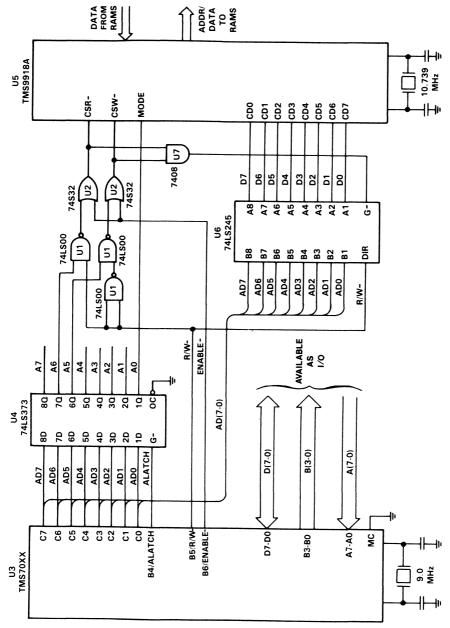

|    |      | 6.1.2     | Peripheral Expansion Mode Example 6                             | -4  |

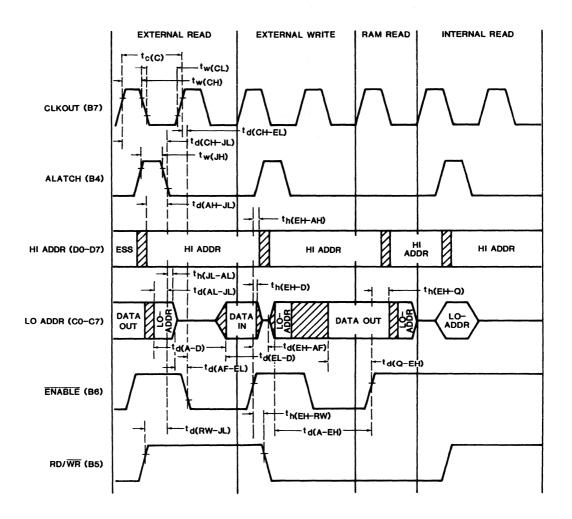

|    |      |           | 6.1.2.1 Read Cycle Timing For The Peripheral Expansion Mode 6   | -4  |

|    |      |           | 6.1.2.2 Write Cycle Timing For The Peripheral Expansion Mode 6. | -5  |

|    |      | 6.1.3     | Microprocessor Mode Example                                     | -7  |

|    |      |           | 6.1.3.1 Read Cycle Timing For The Microprocessor Mode           | -7  |

|    |      |           | 6.1.3.2 Write Cycle Timing For The Microprocessor Mode 6        | -8  |

|    |      | 6.1.4     | Software Considerations                                         | -10 |

|    | 6.2  | Serial C  | Communication With The TMS7000 Family                           | -11 |

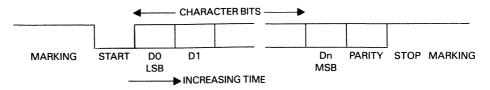

|    |      | 6.2.1     | Communication Formats                                           | -11 |

|    |      | 6.2.2     | Design Constraints For Software And Hardware UART 6             | -12 |

|    |      |           | 6.2.2.1 Design Of A Software UART For The TMS7040 6             | -13 |

|    |      |           | 6.2.2.2 Hardware UART (TMS7041) 6-                              | -25 |

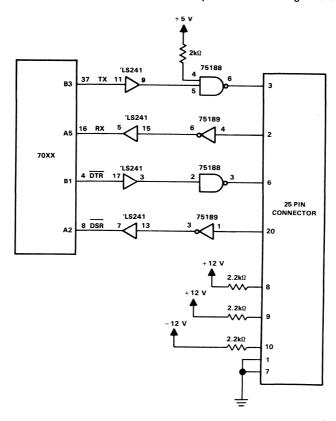

|    |      |           | 6.2.2.3 RS-232-C Interface                                      | -34 |

|    |      |           | 6.2.2.4 Other Design Approach 6-                                | -36 |

|    | 6.3  | Instruct  | tion Set Application Notes                                      | .48 |

|    |      | 6.3.1     | The Status Register                                             | -48 |

|    |      |           | 6.3.1.1 Compare And Jump Instructions 6-                        | .49 |

|    |      |           | 6.3.1.2 Addition And Subrtaction Instructions 6-                | -51 |

|    |      |           | 6.3.1.3 Swap And Rotation Instructions 6-                       | -54 |

|    |      | 6.3.2     | Stack Operations                                                | -56 |

|    |      | 6.3.3     | Subroutine Instructions 6-                                      | .57 |

|    |      | 6.3.4     | Multiply And Shifting                                           | .58 |

|    |      | 6.3.5     | Branch Instructions                                             | 61  |

|    |      | 6.3.6     | Interrupts 6-                                                   | 61  |

|    |      |           |                                                                 | ٠.  |

| 7. |      |           | T SUPPORT TOOLS                                                 |     |

|    | 7.1  | Introdu   | ction                                                           | 1   |

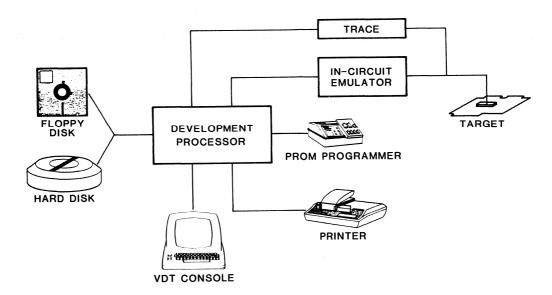

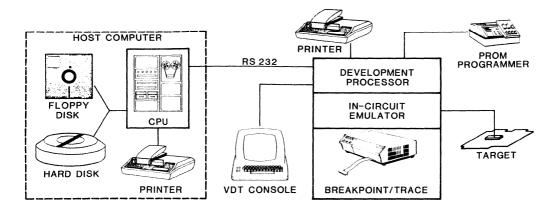

|    |      | 7.1.1     | XDS Concept                                                     | 2   |

|    |      | 7.1.2     | Key Features                                                    | 3   |

|    | 7.2  | CrossW    | /are                                                            | 3   |

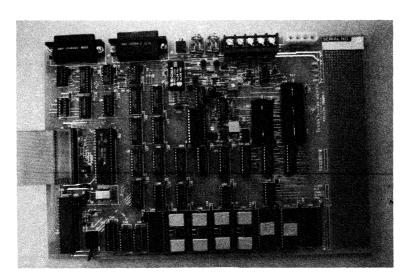

|    | 7.3  | XDS Ha    | ardware                                                         | 3   |

|    |      | 7.3.1     | Model 22                                                        | 4   |

|    |      | 7.3.2     | Model 33                                                        | 4   |

|    |      | 7.3.3     | Differences And Similarities - Model 22/Model 33                | 6   |

|    |      | 7.3.4     | XMPL                                                            | 7   |

|    |      | 7.3.5     | Breakpoint And Trace Functions                                  | 8   |

|    |      | 7.3.6     | Multiprocessing                                                 | 9   |

|    | 7.4  | Evaluati  | ion Modules                                                     | 9   |

|    |      | 7.4.1     | TMS7000 EVM                                                     | 10  |

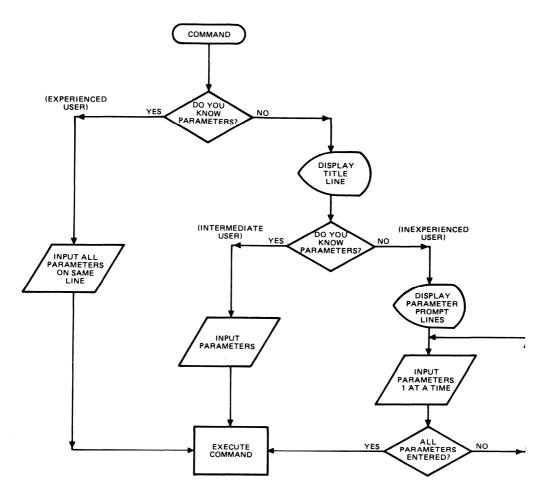

|    |      |           | 7.4.1.1 Operating System                                        | 10  |

|    | 7.5  | Prototy   | pe Component                                                    | 10  |

|    |      | 7.5.1     | SE70P161 Description                                            | 11  |

|    |      |           | 7.5.1.1 Prototyping                                             | 12  |

|    |      |           | 7.5.1.2 TMS7041 Prototyping                                     | 12  |

|    |      |           | 7.5.1.3 TMS7020/TMS7040/TMS70120 Prototyping 7-                 | 12  |

|    |      |           | 7.5.1.4 SE70P161 Electrical Data                                | 12  |

|    | 7.6  | Physical  | I And Ordering Information                                      | 12  |

|    |      | 7.6.1     | CrossWare                                                       | 12  |

|    |      | 7.6.2     | XDS Hardware                                                    | 12  |

|    |      |           | 7.6.2.1 Physical Specifications                                 | 13  |

|              |                                         | 7.6.3<br>7.6.4                                                       | Evaluation Modules              | 7-13<br>7-13                     |

|--------------|-----------------------------------------|----------------------------------------------------------------------|---------------------------------|----------------------------------|

|              |                                         |                                                                      |                                 |                                  |

| 8.           | 1NDEPE<br>8.1<br>8.2                    | Introduct<br>Processo<br>8.2.1<br>8.2.2<br>8.2.3                     | rion                            | 8-3<br>8-3                       |

|              | 8.3                                     | 8.3.1<br>8.3.2                                                       | hley - CP/M Based Support Tools | 8-4<br>8-4                       |

|              | 8.4                                     | SEEQ: Se<br>8.4.1                                                    | elf-Adaptive EEROM              | 8-4                              |

| 9.           | QUAL<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5 | Introduc<br>Average<br>New Pro<br>Reliabilit                         | don                             | 9-2                              |

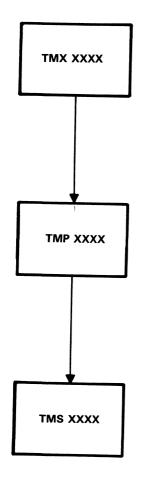

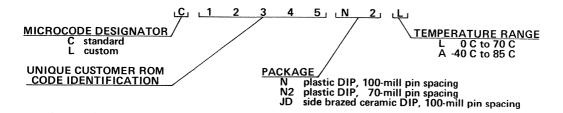

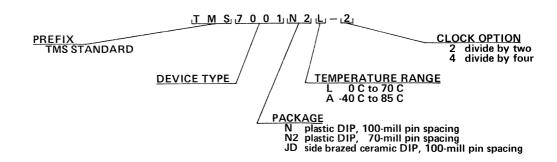

| 10.          | GENE<br>10.1                            | RAL INFO<br>TMS700<br>10.1.1<br>10.1.2<br>10.1.3<br>10.1.4<br>10.1.5 | RMATION  OO Family Devices      | 10-6                             |

|              | 10.2                                    | Develop<br>10.2.1<br>10.2.2<br>10.2.3                                | oment Support Tools             | 10-10<br>10-10<br>10-10<br>10-10 |

|              | 10.3<br>10.4                            | TMS70<br>Worldw                                                      | 00 Family Documentation         | 10-10                            |

|              |                                         |                                                                      | APPENDICES                      |                                  |

| APPE         | NDIX                                    |                                                                      |                                 | PAGE                             |

| Appe<br>Appe | ndix B 1                                | ГМS7000<br>ГМS7500                                                   | Bus Activity Chart              | B-1<br>C-1                       |

# LIST OF ILLUSTRATIONS

| FIGUR | E                                                    | PAGE |

|-------|------------------------------------------------------|------|

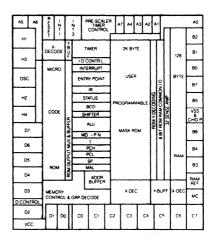

| 1-1   | TMS7020 Microcomputer Bar Plan                       | 1-3  |

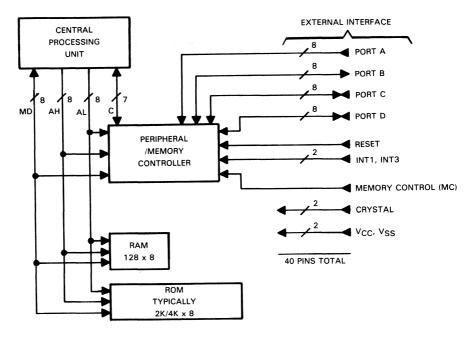

| 2-1   | TMS7000 Internal Architecture                        |      |

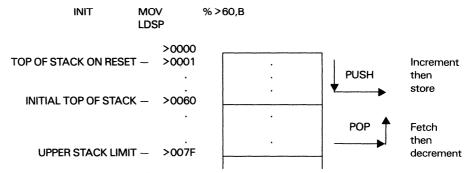

| 2-2   | Example Of Stack Initialization In the Register File |      |

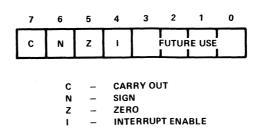

| 2-3   | Status Register (ST)                                 |      |

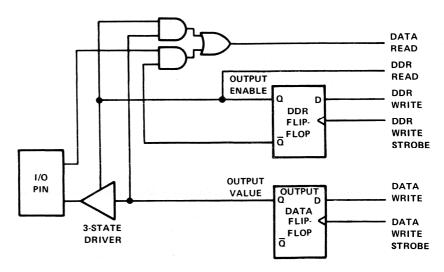

| 2-4   | Bidirectional I/O Logic                              |      |

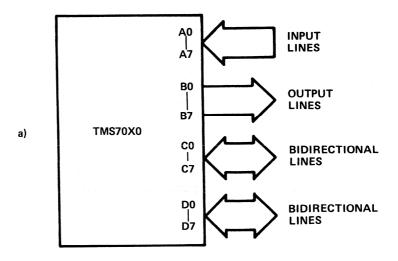

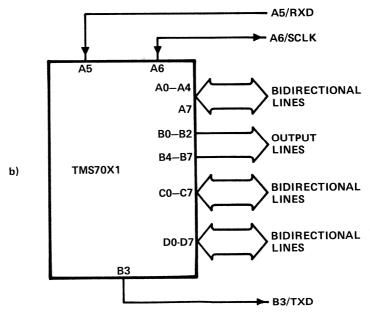

| 2-5   | I/O Ports: Single-Chip Mode                          |      |

| 2-6   | Interrupt Generation: System Emulator Mode           | 2-15 |

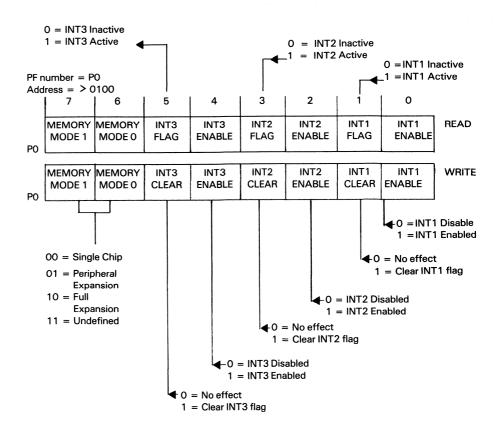

| 2-7   | IOCNTO - I/O Control Register 0                      | 2-17 |

| 2-8   | IOCNT1 - I/O Control Register 1                      | 2-18 |

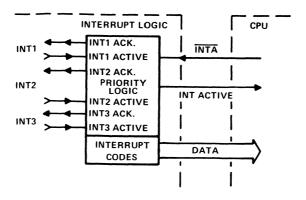

| 2-9   | CPU Interface To Interrupt Logic                     |      |

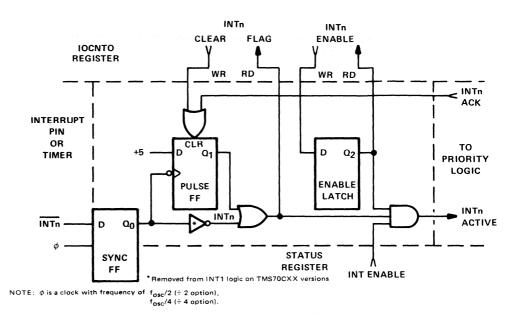

| 2-10  | Interrupt Logic                                      |      |

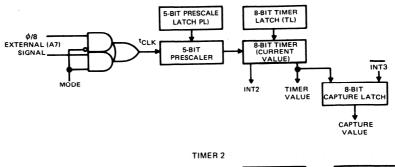

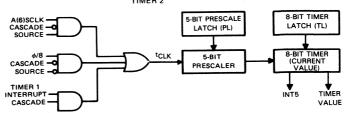

| 2-11  | Programmable Timer/Event Counter                     | 2-25 |

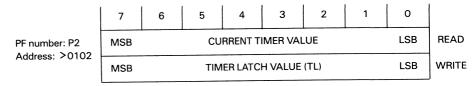

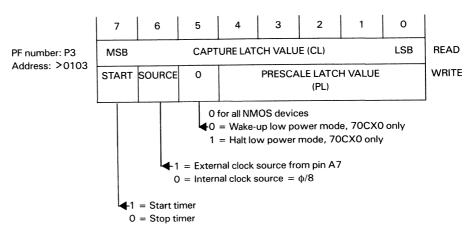

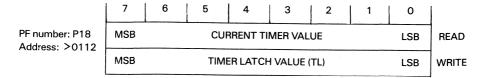

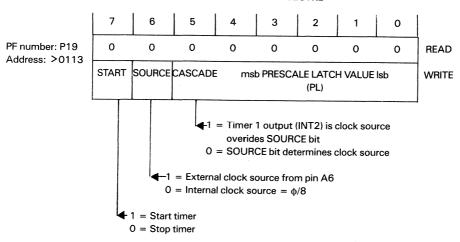

| 2-12  | Timers 1 & 2 Data And Control Registers              | 2-25 |

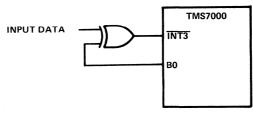

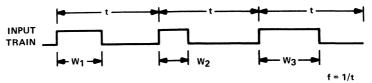

| 2-13  | Pulse Width Measurement                              |      |

| 2-14  | Pulse Width Modulated Pulse Train                    |      |

| 2-15  | TMS7000 PWM INT3 Timing                              |      |

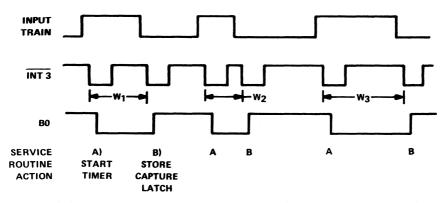

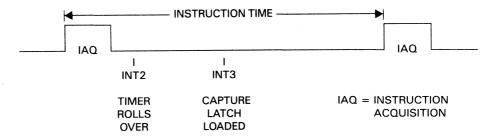

| 2-16  | Simultaneous Interrupts, INT2 Preceding              | 2-31 |

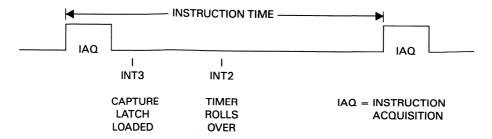

| 2-17  | Simultaneous Interrupts, INT3 Preceding              | 2-32 |

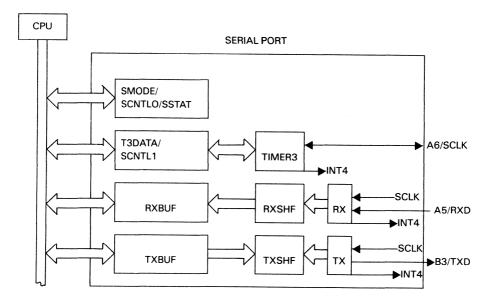

| 2-18  | Serial Port Functional Blocks                        | 2-34 |

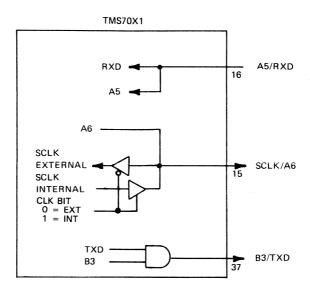

| 2-19  | Serial Port I/O Logic                                |      |

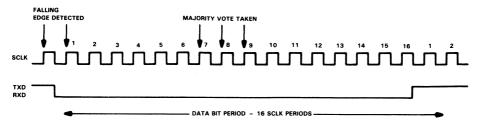

| 2-20  | Asynchronous Communication Format                    |      |

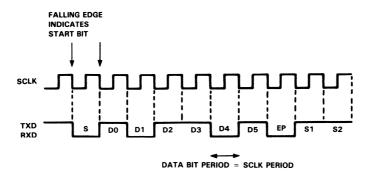

| 2-21  | Isosynchronous Communication Format                  |      |

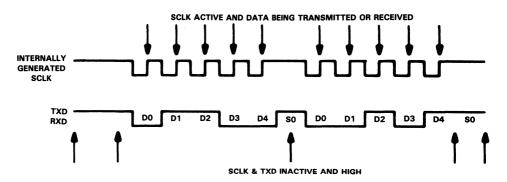

| 2-22  | Serial I/O Communication Format                      |      |

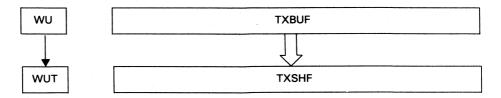

| 2-23  | Double Buffered WUT And TXSHF                        |      |

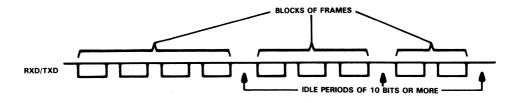

| 2-24  | Motorola Multiprocessor Communication Format         |      |

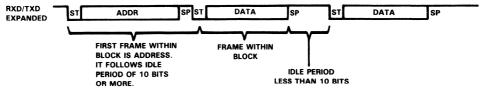

| 2-25  | Intel Multiprocessor Communication Format            |      |

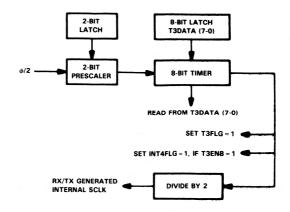

| 2-26  | TIMER 3 Block Diagram                                |      |

| 2-27  | Serial Mode Register - SMODE                         |      |

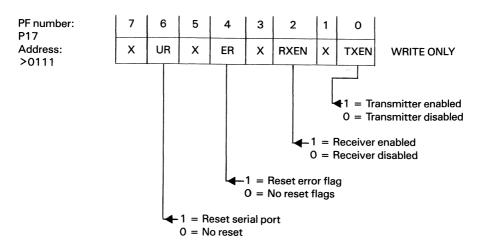

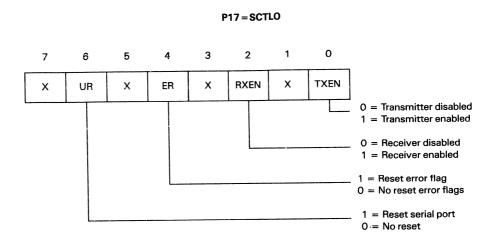

| 2-28  | Serial Control O Register - SCTLO                    | 2-44 |

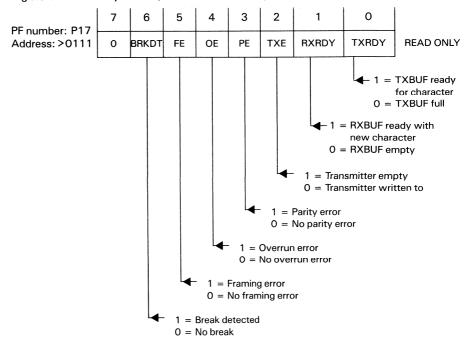

| 2-29  | Serial Port Status Register - SSTAT                  | 2-45 |

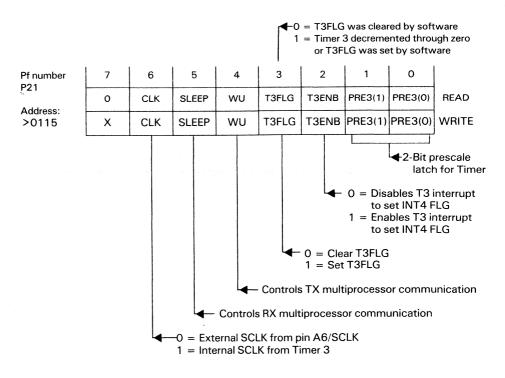

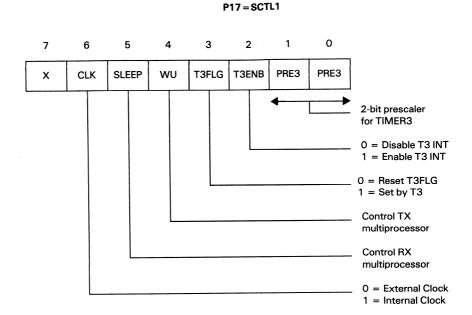

| 2-30  | Serial Control 1 Register - SCTL1                    | 2-47 |

| 2-31  | Timer 3 Data Register - T3DATA                       |      |

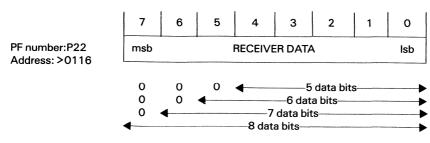

| 2-32  | Receiver Buffer - RXBUF                              | 2-48 |

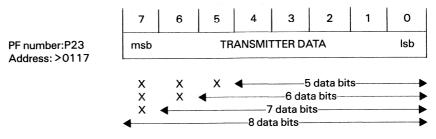

| 2-33  | Transmitter Buffer - TXBUF                           | 2-49 |

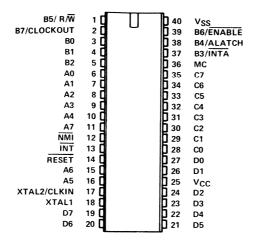

| 2-34  | SC, PE, FE, And Microprocessor Pin Assignments       | 2-52 |

| 2-35  | System Emulator Mode Pin Assignments                 | 2-54 |

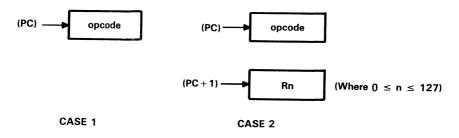

| 3-1   | Single Register Addressing Mode Object Code          | 3-4  |

| 3-2   | Register File Addressing Mode Object Code            |      |

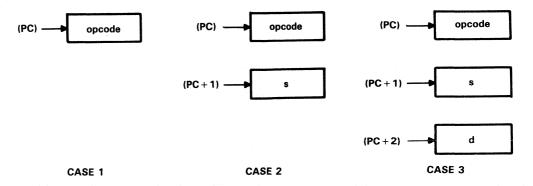

| 3-3   | Peripheral File Addressing Mode Object Code          | 3-5  |

| 3-4   | Immediate Addressing Mode Object Code                | 3-6  |

| 3-5   | Program Counter Relative Addressing Mode Object Code | 3-6  |

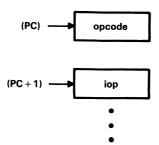

| 3-6   | Direct Memory Addressing Mode Object Code            | 3-7  |

| 3-7   | Register File Indirect Addressing Mode Object Code   |      |

| 3-8   | Indexed Addressing Mode Object Code                  | 3-8  |

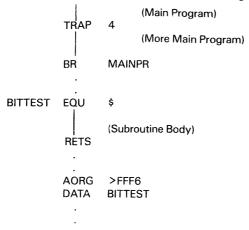

| 3-9   | Trap Vector Table                                    |      |

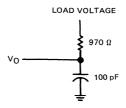

| 4-1   | Output Loading Circuit For Test                      |      |

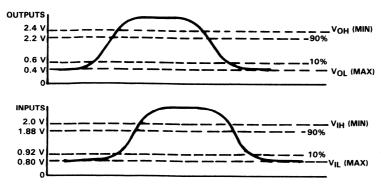

| 4-2   | Measurement Points For Switching Characteristics     |      |

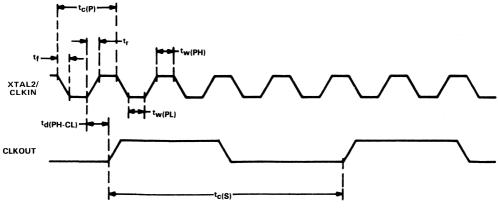

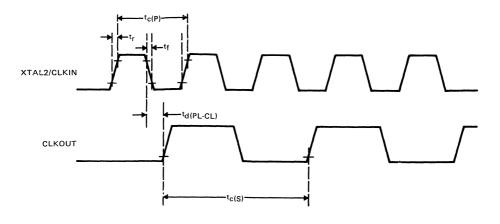

| 4-3   | Clock Timing                                         |      |

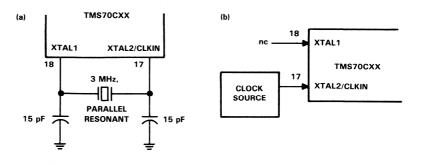

| 1-1   | Recommended Clock Connections                        |      |

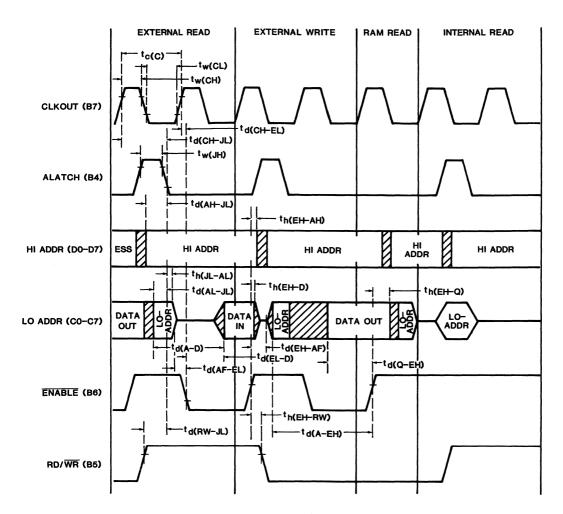

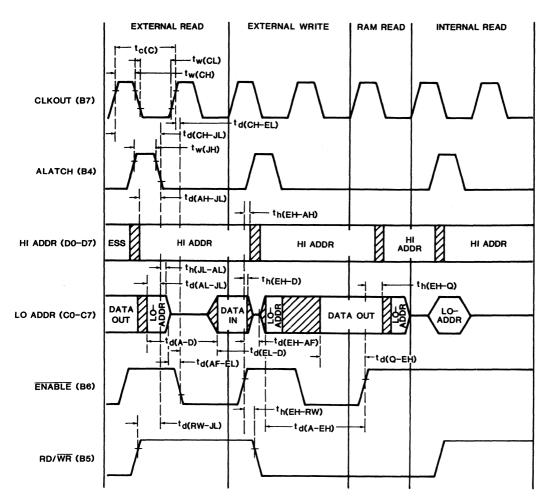

| 4-5          | Read and Write Cycle Timing                                   | 4-6    |

|--------------|---------------------------------------------------------------|--------|

| 4-6          | Ceramic Resonator Circuit                                     | 4-/    |

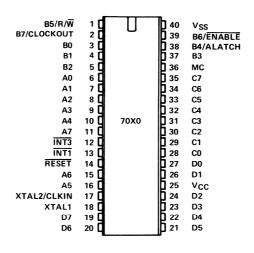

| 4-7          | SC, FE, PE, and Microprocessor Mode Pin Assignments (TMS7000) | 4-14   |

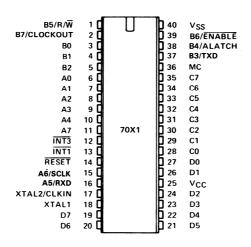

| 4-8          | SC, FE, PE, and Microprocessor Mode Pin Assignments (TMS7001) | 4-15   |

| 4-9          | Output Loading Circuit For Test                               | 4-19   |

| 4-10         | Clock Timing                                                  | 4-20   |

| 4-11         | Measurement Points For Switching Characteristics (VDD = 5V)   | 4-20   |

| 4-12         | Read And Write Cycle Timing                                   | 4-22   |

| 4-13         | Recommended Clock Connections                                 | 4-23   |

| 4-14         | SC, FE, PE, and Microprocessor Mode Pin Assignments           | 4-24   |

| 4-15         | Read And Write Cycle Timing                                   | 4-29   |

| 5-1          | TMS7000 CPU Internal Block Diagram                            | 5-4    |

| 5-2          | Assembly Language Multiply Sequence                           | 5-5    |

| 5-3          | Non-Core Assembly Language Instructions                       | 5-6    |

| 5-4          | Microcode Development Flowchart                               | 5-7    |

| 5-5          | TMS7000 Family Address Space                                  | 5-16   |

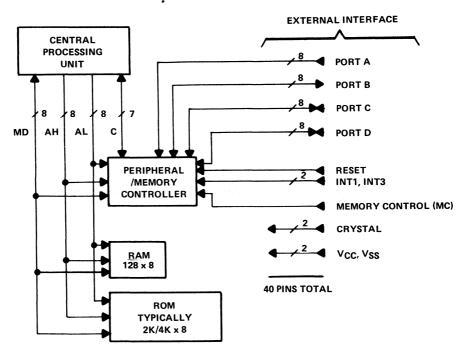

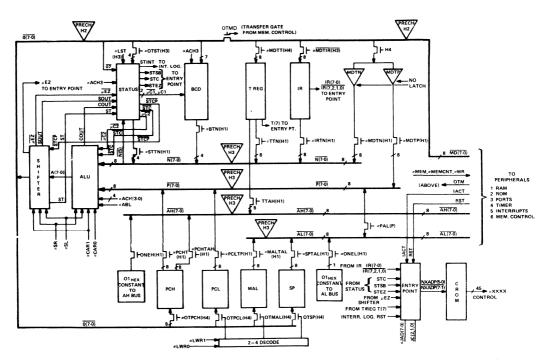

| 5-6          | TMS7000 Overall Block Diagram                                 | 5-17   |

| 5-7          | Sample Of A Micasm Statement                                  | . 5-20 |

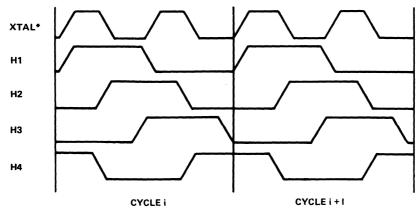

| 5-8          | Microinstruction Cycle Phases                                 | . 5-20 |

| 5-9          | On-Chip RAM Memory Cycle Timing                               | . 5-22 |

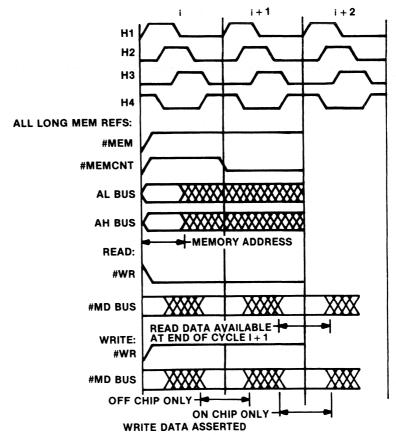

| 5-10         | Long Memory Cycle Timing                                      | . 5-23 |

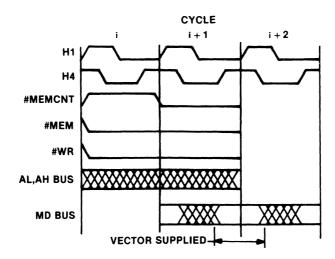

| 5-11         | Interrupt Vector Reads                                        | . 5-24 |

| 5-12         | Interrupt Vector References                                   | . 5-25 |

| 5-13         | Internal Organization Of The TMS7000 CPU                      | . 5-27 |

| 5-14         | P Bus Sources                                                 | . 5-28 |

| 5-15         | N Bus Sources                                                 | . 5-28 |

| 5-16         | AL Bus Sources                                                | . 5-29 |

| 5-17         | AH Bus Sources                                                | . 5-30 |

| 5-18         | Lowwrite (1-0) Description                                    | . 5-30 |

| 5-19         | O Bus Destinations                                            | . 5-31 |

| 5-20         | MD Bus Destinations                                           | . 5-32 |

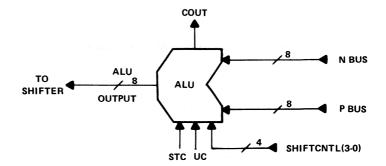

| 5-21         | ALU Block Diagram                                             | . 5-33 |

| 5-22         | ALU Functions                                                 | . 5-33 |

| 5-23         | ALU Carry In Values                                           | . 5-34 |

| 5-24         | Microcode Example                                             | . 5-35 |

| 5-25         | SHIFT/ALU Carry-In Controls                                   | . 5-36 |

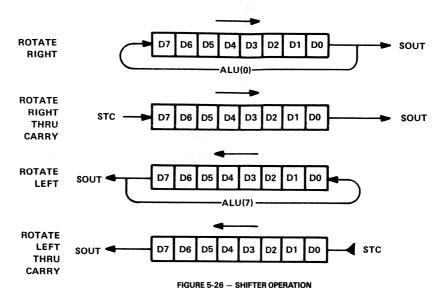

| 5-26         | Shifter Operation                                             | . 5-37 |

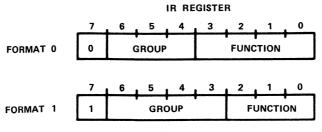

| 5-27         | IR Register Formats                                           | . 5-38 |

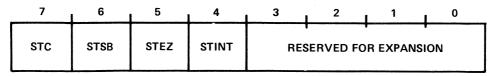

| 5-28         | Status Register                                               | . 5-38 |

| 5-29         | ST Register Sources                                           | . 5-39 |

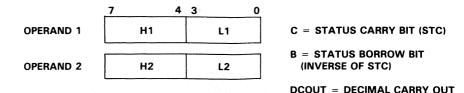

| 5-30         | BCD Correction Constant Generation                            | . 5-41 |

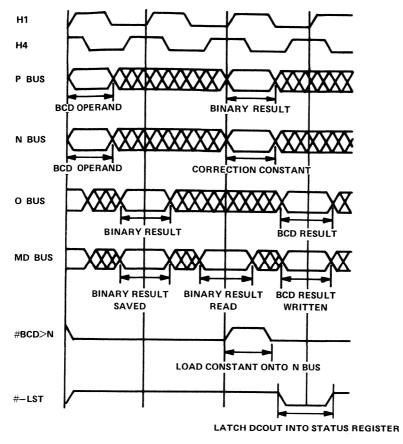

| 5-31         | BCD Arithmetic Operation Timing                               | . 5-42 |

| 5-31         | MICASM Statement                                              | . 5-43 |

| 5-32         | Microinstruction Dispatch Example                             | . 5-44 |

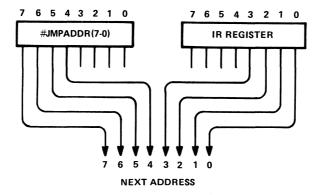

| 5-34         | Next MICRO Address Generation                                 | . 5-45 |

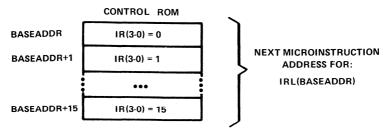

| 5-35         | IRL Dispatch                                                  | . 5-46 |

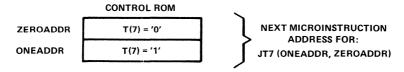

| 5-36         | JT7 Dispatch                                                  | . 5-46 |

| 5-36         | JUZ Dispatch                                                  | . 5-47 |

| 5-37         |                                                               | . 5-47 |

| 5-38         |                                                               | 5-48   |

| 5-39<br>5-40 |                                                               | 5-49   |

| 5-40<br>5-41 | JC DISPATCH                                                   | . 5-50 |

| 5-41<br>5-42 |                                                               | 5-50   |

| 5-42         | iviacro Jump Conditions                                       | . 5 50 |

| 6-4   | Microprocessor Mode Example .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6.0         |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 6-5   | Asynchronous Communication Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-9<br>6-11 |

| 6-6   | I/O*Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0-11        |

| 6-7   | SWXMIT Routine Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6 17        |

| 6-8   | SWCRVD Routine Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-17        |

| 6-9   | Delay Constants Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0-20        |

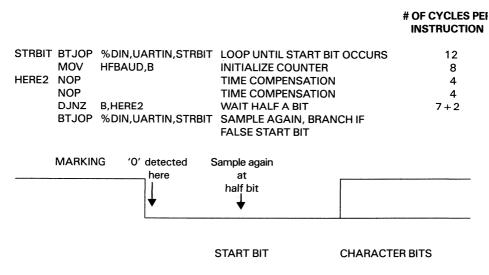

| 6-10  | Start Bit Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0-21        |

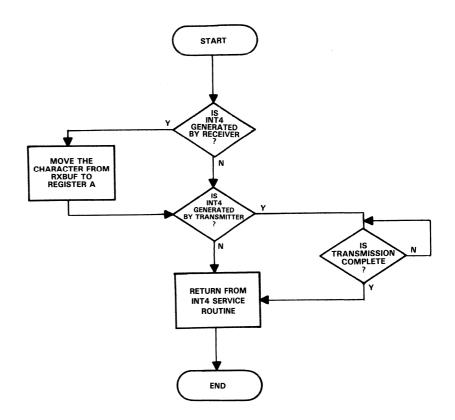

| 6-11  | Interrupt 4 Service Routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0-22        |

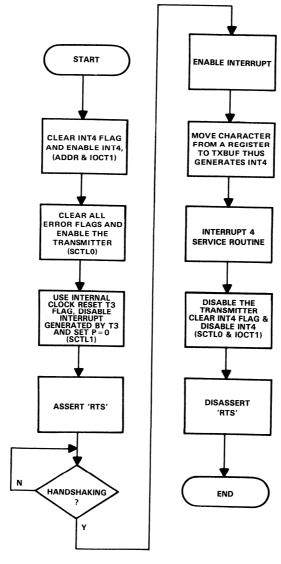

| 6-12  | HWXMIT Routine Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0-31        |

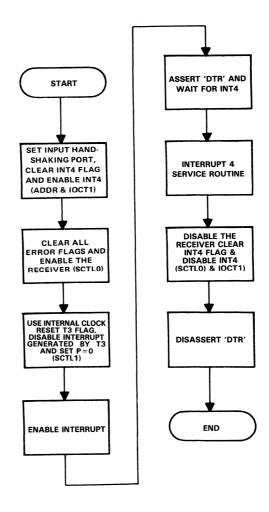

| 6-13  | HWRCVD Routine Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0-32        |

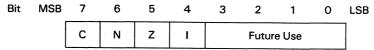

| 6-14  | Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0-33        |

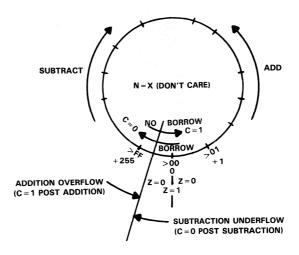

| 6-15  | Unsigned System With 8 Bits Of Magnitude: 0-255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0-48        |

| 6-16  | Signed System With 7 Bits Of Magnitude: -127 TO +127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0-53        |

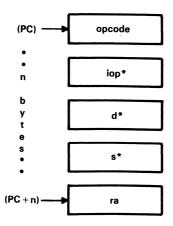

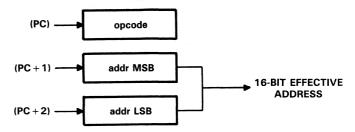

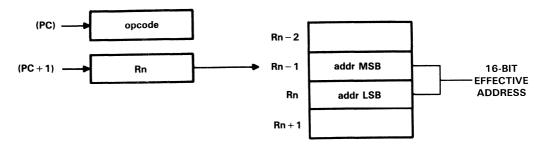

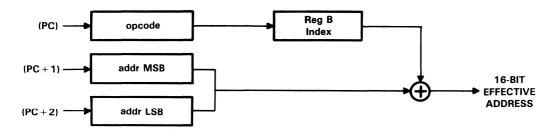

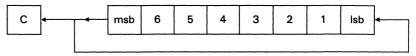

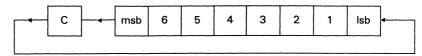

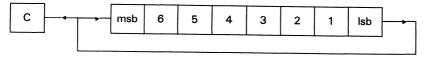

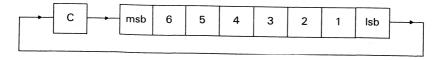

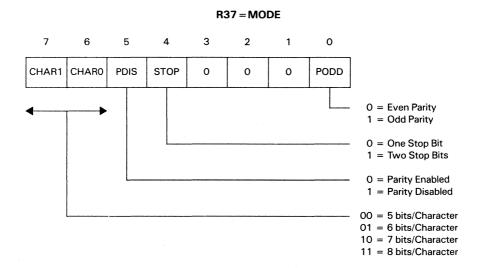

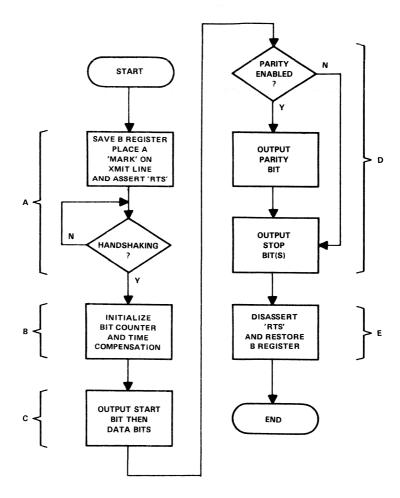

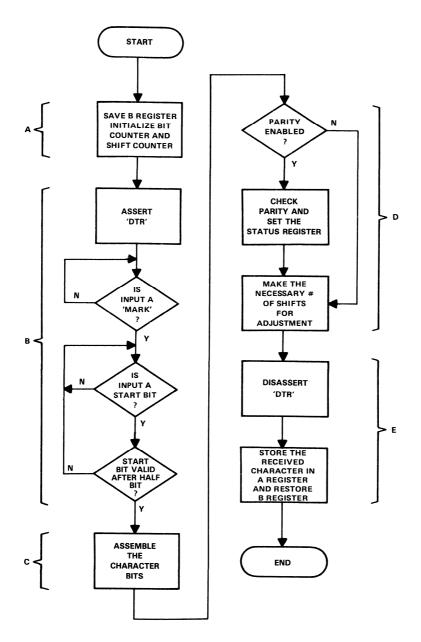

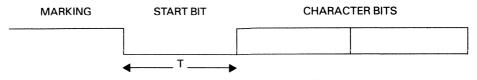

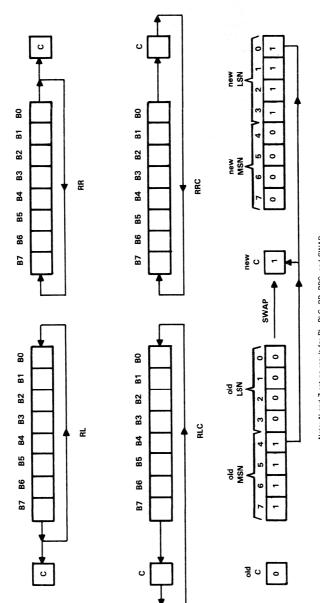

| 6-17  | SWAP And Rotation Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-53        |